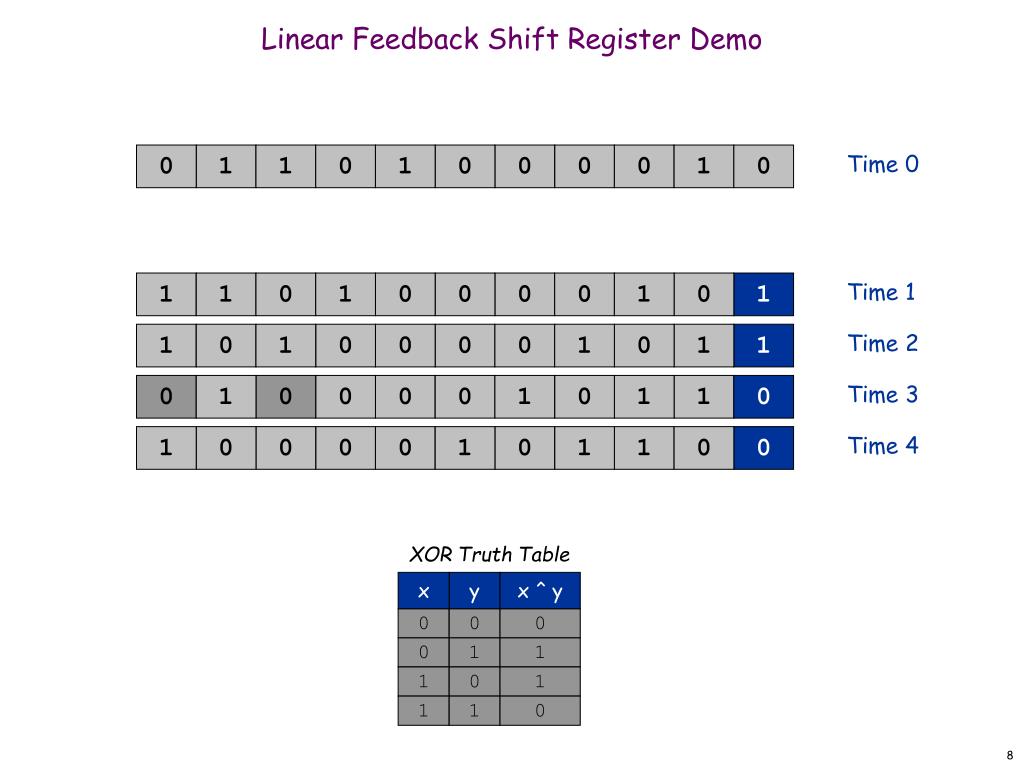

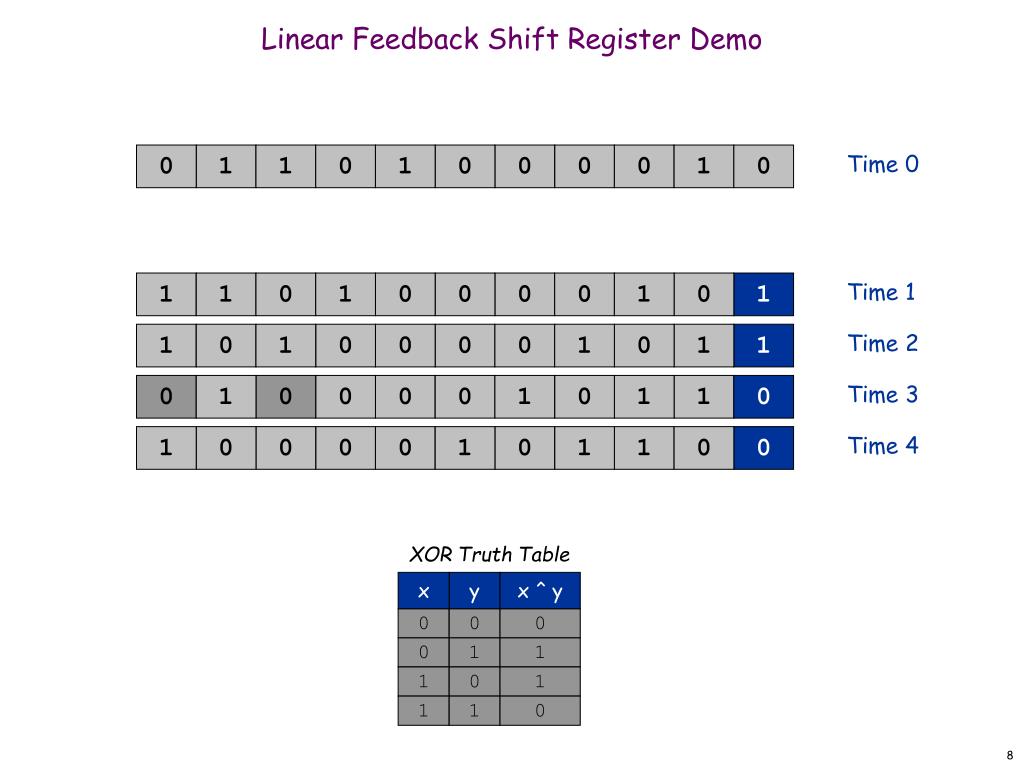

The sequence of bits in the rightmost position is called the output stream.

The taps are XOR'd sequentially with the output bit and then fed back into the leftmost bit. The rightmost bit of the LFSR is called the output bit. The bit positions that affect the next state are called the taps. The state ACE1 hex shown will be followed by 5670 hex. The feedback tap numbers in white correspond to a primitive polynomial in the table so the register cycles through the maximum number of 65535 states excluding the all-zeroes state.

5.3 Uses in digital broadcasting and communicationsĪ 16-bit Fibonacci LFSR. Both hardware and software implementations of LFSRs are common. However, an LFSR with a well-chosen feedback function can produce a sequence of bits which appears random and which has a very long cycle.Īpplications of LFSRs include generating pseudo-random numbers, pseudo-noise sequences, fast digital counters, and whitening sequences. Likewise, because the register has a finite number of possible states, it must eventually enter a repeating cycle. The initial value of the LFSR is called the seed, and because the operation of the register is deterministic, the stream of values produced by the register is completely determined by its current (or previous) state. The only linear function of single bits is xor, thus it is a shift register whose input bit is driven by the exclusive-or (xor) of some bits of the overall shift register value. The maximal sequence consists of every possible state except the "0000" state.Ī linear feedback shift register (LFSR) is a shift register whose input bit is a linear function of its previous state. The XOR gate provides feedback to the register that shifts bits from left to right.

Template:Redirect Template:Refimprove Template:No footnotes File:LFSR-F4.GIFĪ 4-bit Fibonacci LFSR with its state diagram.

0 kommentar(er)

0 kommentar(er)